<--- Back to Details

| First Page | Document Content | |

|---|---|---|

Date: 2008-12-11 11:26:08Compiler optimization Cycles per instruction DEC Alpha PA-8000 Clock signal SunOS AMD 10h Intel 80486 Computer architecture Computer hardware SPARCstation |

Add to Reading List |

| 82596CA HIGH-PERFORMANCE 32-BIT LOCAL AREA NETWORK COPROCESSOR Y Performs Complete CSMA/CD MediumDocID: 1a5WF - View Document |

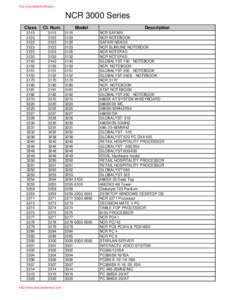

| The Core Memory Project NCR 3000 Series Class Cl. Num.DocID: 15pEz - View Document |

| Preliminary Product Information PC/II+dL 586 Main Street, Glen Williams, Ontario, L7G 3T6 Canada Phone: (DocID: 13wWb - View Document |

| Product Information PC/II+dxe 586 Main Street, Glen Williams, Ontario, L7G 3T6 Canada Phone: (DocID: 13wM0 - View Document |

| Product Information PC/II+dx 586 Main Street, Glen Williams, Ontario, L7G 3T6 Canada Phone: (DocID: 13tad - View Document |

mhz: Anatomy of a micro-benchmark Carl Staelin Hewlett-Packard Laboratories Larry McVoy BitMover, Inc.

mhz: Anatomy of a micro-benchmark Carl Staelin Hewlett-Packard Laboratories Larry McVoy BitMover, Inc.