<--- Back to Details

| First Page | Document Content | |

|---|---|---|

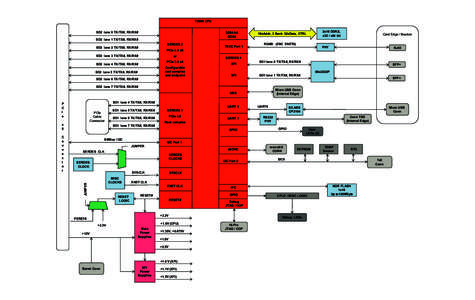

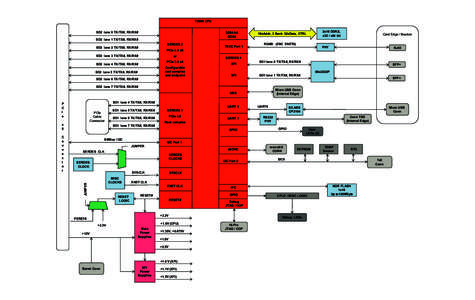

Date: 2014-09-16 22:23:28Computer buses PCI Express Embedded systems XFP transceiver SerDes Joint Test Action Group MBus Rx Electronic engineering Electronics Computer hardware |

Add to Reading List |

| First Page | Document Content | |

|---|---|---|

Date: 2014-09-16 22:23:28Computer buses PCI Express Embedded systems XFP transceiver SerDes Joint Test Action Group MBus Rx Electronic engineering Electronics Computer hardware |

Add to Reading List |